处理器支持

Intel X86

介绍

本部分包含openPOWERLINK协议栈运行在Intel X86上的文档。

条件

openPOWERLINK运行于Intel X86上支持的操作系统:

- Linux (\ref page_platform_linux)

- Windows (\ref page_platform_windows)

Xilinx Microblaze

介绍

本部分包含openPOWERLINK协议栈运行于Xilinx Microblaze上的文档。使用openMAC IP核,一个优化的POWERLINK协议MAC。 此IP还带有一个可带几个控制节点的菊花链结构的集线器。

内容

- FPGA 设计带有Microblaze CPU和openMAC IP核.

- 数字I/0端口:4 x 8Bit.\n 直接(输入或输出)通过应用软件定义。

性能数据

- 最小循环时长:400 us

- PReq-PRes延迟: 1 us

- 处理数据:4字节输入和4字节输出。

- 支持1 RPDO和1 TPDO。

约束条件

开发板

带有一个Xilinx Spartan6 FPGA和适当的openPOWERLINK需要的周边设备组成的开发板。下面的 Xilinx板很适合运行openPOWERLINK协议栈。

Avnet Spartan6 POWERLINK Evaluation Board

该板来自于Avnet,设计用于运行nPOWERLINK协议栈,可参考: http://www.em.avnet.com/en-us/design/drc/Pages/Xilinx-Spartan6-FPGA-Ethernet-Powerlink-Kit.aspx

执行下述步骤调整板载硬件的安装:

- 连接下述线缆:

- 连接电源到连接器CON600或CON601.

- 'Digilent USB Jtag' (CON101)和主机PC间连上USB线。

- 'Jtag Uart' (CON100)和主机PC间连上USB线。

- J400或者J401上的以太网座与主机以太网口间连上网线。

- 设置下述跳线

- J500的2-3针脚连上跳线.

- J501的2-3针脚连上跳线

- Install jumper on J502的1-2, 4-5和3-6针脚间连上跳线.

- 设置节点开关(SW500和SW501)到一个有效值。

POWERLINK网络

- POWERLINK网络带管理节点(MN)

- openPOWERLINK管理节点,例如:Linux

- B&R POWERLINK管理节点

- 其它POWERLINK管理节点

工具

Xilinx ISE

评估一个基于Xilinx FPGA的openPOWERLINK从站需要下列工具:

Xilinx ISE - Embedded Edition叫做ISE Design Suite - 14.7 Full Product Installation或ISE Design Suite - 14.7 Embedded Edition,能够从: http://www.xilinx.com/support/download/index.htm下载。授权可以从`Xilinx Licensing Site`获得,评估板(30天)免费。

CMake

创建openPOWERLINK协议栈和demo应用需要使用开源的交叉编译工具CMake。 (http://www.cmake.org). CMake版本要求 V2.8 或更高。

CMake详细描述见 cmake section.

TeraTerm

TeraTerm是一个串口通信文本打印输出程序。开源并可下载于: http://ttssh2.sourceforge.jp/

openPOWERLINK协议栈组件

下面这段内容包含了Microblaze系统上可用的openPOWERLINK components描述。 system.

协议栈库

openPOWERLINK协议栈分为用户和内核两部分。目标平台Microblaze上可用如下配置:

Direct Link to Application

内核部分直接连接到用户部分和应用(完整库)成为一个独立的可执行文件。

Libraries:

stack/proj/generic/liboplkcn(liboplkcn.a)

Demo应用

下列demo应用提供给Microblaze:

创建

为Microblaze创建openPOWERLINK遵循generic build instructions并且执行该节所有创建步骤。在Xilinx Microblaze平台上可实施以下build步骤 :

- Build the hardware platform

- Build the openPOWERLINK stack libraries

- Build your application (or a delivered demo application)

运行openPOWERLINK

为了下载FPGA配置和应用可执行文件到目标平台,需执行下述步骤:

打开

ISE Design Suite Command Prompt执行下列命令:> cd <openPOWERLINK_directory>\bin\generic\microblaze\[BOARD_NAME]\[DEMO_NAME] > make download-bits > make download-elf使用终端程序查看debug输出(仅在应用编译为debug模式)

- Baud rate:

9600 - Data Bits:

8 - Stop Bits:

1 - Parity:

none - Flow control:

none

- Baud rate:

调试

可以通过使用Xilinx工具Xilinx Software Development Kit (SDK)调试带GNU debugger的用户应用。因此,重点在应用工程编译的CMake变量CMAKE_BUILD_TYPE置Debug!

CMake已为所有协议栈子工程生成了Eclipse (SDK)工程文件。可以导入当前工作空间:\n

Import -> General -> Existing Project into Workspace。

选择协议栈根目录以便导入和选择你的demo所需的所有工程。下列工程可用:\n

- 带比特流的硬件平台

- 板支持包BSP

- 你的应用工程。例: demo-cn-embedded.

- 协议栈库工程。例: oplkcn. (导入此工程是可选的!)

- omethlib驱动库。(导入此工程是可选的!)

在你的demo工程demo-cn-embedded导入后使用:\n

Run -> Debug As -> Launch on Hardware 启动调试,单步执行代码。

怎样向本地flash写入程序

要求: 所有\ref sectxilinxbuild步骤完成且二进制文件安装到__bin目录。

打开

ISE Design Suite Command Prompt执行下列命令:> cd <openPOWERLINK_dir>/contrib/bootloader/xilinx-microblaze/simpleboot/build > cmake -G"Unix Makefiles" -DCMAKE_TOOLCHAIN_FILE=../../../../../cmake/toolchain-xilinx-microblaze-gnu.cmake ../ > cmake -DCFG_BIN_DIR=../../../../../bin/generic/microblaze/avnet-s6plkeb/cn-single-gpio -DCFG_HW_LIB_DIR=../../../../../hardware/lib/generic/microblaze/avnet-s6plkeb/cn-single-gpio ../ > make all > make prog-flash

这些命令为你的demo build了bootloader并生成了可写入本地flash的image。注意更改变量

CFG_BIN_DIR和CFG_HW_LIB_DIR以便为其它的例程build bootloader。

配置选项

如果需要更改配置选项,在命令行配置(-DCFG_XXX=XXX)。

CFG_BIN_DIR

你的POWERLINK例程安装路径(例:

<openPOWERLINK_dir>/bin/generic/microblaze/avnet-s6plkeb/cn-single-gpio)CFG_HW_LIB_DIR

你的POWERLINK例程的硬件工程 安装路径。(例:

<openPOWERLINK_dir>/hardware/lib/generic/microblaze/avnet-s6plkeb/cn-single-gpio)

怎样使用MN配置文件

MN配置文件mnobd.cdc需保存于文件系统。Microblaze demos无文件系统,因而,需要生成mnobd_char.txt文件(\ref sect_openconfig_generate_char_file)。

Xilinx Zynq SoC上的openPOWERLINK

介绍

本部分内容为Xilinx Zynq SoC上的openPOWERLINK协议栈。在Zynq上,openPOWERLINK能够运行于 Linux下,也能够运行于嵌入式无系统环境下。本部分将给出支持的环境说明,展示在Zynq SoC上build和运行openPOWERLINK的步骤。

当前,openPOWERLINK可在Zynq SoC上运行于下列环境:

Linux on Zynq ARM openPOWERLINK运行于Linux上,此Linux运行ARM processing system (PS) of the SoCprocessor under Linux.

Dual - Processor No-OS solution (ARM/FPGA) 时间临界的协议栈内核部分运行于Zynq SoC的Microblaze软件处理器可编程逻辑(PL)。协议栈应用部分运行于SoC的ARM Cortex A9 Core 0 processing system (PS)。

要求

开发板

- Xilinx ZC702开发套件。

- 其它带Zynq 7000 series SoC的板子。

POWERLINK网络

带一个控制节点(CN)的POWERLINK网络

- openPOWERLINK控制节点,例: Linux

- B&R POWERLINK控制节点

带一个管理节点(MN)的POWERLINK网络

- openPOWERLINK管理节点,例:Linux

- B&R POWERLINK管理节点

工具

Xilinx ISE

下列工具用于基于Xilinx Zynq的openPOWERLINK解决方案:

Xilinx ISE - Embedded Edition叫做ISE Design Suite - 14.7 Full Product Installation或ISE Design Suite - 14.7 Embedded Edition,可以下载自:http://www.xilinx.com/support/download/index.htm。30天评估版可以从`Xilinx Licensing Site`获得,评估版免费。

单独BSP V3.11.a补丁

ARM Cortex 9 standalone BSP V3.11.a 带ISE的版本有一个数据缓冲处理bug。由于无法正确的更改数据缓存,造成ARM Cortex 9和Microblaze软核间通信数据不一致。

Xilinx提供了一个补丁,位于: http://www.xilinx.com/support/answers/60671.html

按照说明为Xilinx ISE安装包standalone BSP打上补丁:

- 从给出的链接地址下载ar60671.zip:(直接链接: http://www.xilinx.com/Attachment/ar60671.zip)

- 在Xilinx安装路径找到有错误的standalone BSP:

<XILINX_ISE_PATH>/EDK/sw/lib/bsp/standalone_v3_11_a - 备份Xilinx安装包中的standaloneBackup the standalone BSP:

- 从下载的zip文件中解压BSP(

xps/bsp/standalone_v3_11_a)并拷贝进安装目录代替存在的文件和目录。

CMake

为了创建openPOWERLINK协议栈和demo应用,需要使用开源交叉平台构建工具CMake(http://www.cmake.org)。版本V2.8.7或更高。

详细描述请看cmake section.

libpcap Library

为了在Linux下使用用户空间POWERLINK协议栈,需要使用libpcap库来访问以太网接口。

注意: 为了能和Zynq SoC demo一起工作,libpcap库需要交叉编译为ARM目标平台。

终端软件

需要一个终端软件通过串口与设备交互。提供控制台访问(键盘输入,文本输出)系统。

Minicom是个开源的终端软件,Debian或者Ubuntu用户通过apt-get获得:

> sudo apt-get install minicom

TeraTerm是一个通过串口传输打印输出字符的程序。它开源并可下载自 http://ttssh2.sourceforge.jp/

Linux 内核

为了在Linux上运行openPOWERLINK,需要为Zynq platform提供Linux内核。 Zynq平台可用的Linux内核位于github上,可以下载或克隆于:https://github.com/Xilinx/linux-xlnx.

github上Linux内核版本3.10作为xilinx-v14.7使用,在本文档编写时正在测试。

为Zynq交叉编译Linux的步骤和其它可用库的信息可查询:http://www.wiki.xilinx.com/Zynq+Linux.

Zynq ARM上的Linux

在Zynq Soc上,openPOWERLINK运行于Soc的ARM Cortex A9 processing system (PS)的Linux上。下面这段包含了一些在Zynq Soc上基于Linux的openPOWERLINK应用的一些额外信息。 Linux上运行openPOWERLINK的常用信息请参考 "openPOWERLINK on Linux".

注意:第三方库如libpcap何libqt等,独立于openPOWRLINK,也需要经过Zynq ARM的交叉编译。

内容

下列模块需要加入openPOWERLINK以支持Zynq SoC:

- Zynq 7000 series SoCs (emacps)上的Gigabit以太网控制器所需Edrv模块。

- Zynq 7000 series SoCs上的三倍定时计数器所需高分辨率定时模块。

openPOWERLINK协议栈组件

此段是可用openPOWERLINK组件描述。

协议栈库

请参考Linux协议栈库关于Linux上的可用协议栈库信息。

Demo应用

Linux支持下述demo应用:

驱动

请参考[Linux驱动] (\ref sect_linux_components_drivers)相关的可用驱动信息。

创建

Zynq ARM的Linux下交叉编译openPOWERLINK请参考常规创建说明并执行所有该部分要求的创建步骤。下列build步骤可用于Zynq ARM上的Linux下:

运行openPOWERLINK

下述段落将展示在Zynq ARM上的Linux系统下运行openPOWERLINK所需步骤。

Linux MN/CN控制台 demo

为了在Zynq ARM上运行openPOWERLINK Linux demo应用,请遵循下列步骤:

- 为boot-up准备SD卡:

- uImage : Linux kernel image

- uramdisk.image.gz : Initramfs file

- devicetree.dtb : Device tree blob

- boot.bin : Zynq boot image (generated using first stage bootloader(fsbl.elf),

u-boot binary (u-boot-elf) and system.bit)

- 协议栈二进制文件复制到SD卡上。

- 串口连接主机和Zynq板。

- 使用终端程序连接Zynq上的Linux控制台。

- 启动应用,参考[运行openPOWERLINK于Linux上] (\ref sect_linux_running).

Zynq SoC non-OS FPGA系统

openPOWERLINK在Zynq SoC无嵌入式操作系统环境下也能运行。 此种情况时序严格协议栈的内核部分将运行于Zynq SoC programming logic (PL)的Microblaze软处理器中。协议栈应用部分将运行于SoC的ARM Cortex A9 Core 0 processing system (PS)上。它们之间的通信使用带中断的DDR3共享内存。下面的内容是openPOWERLINK无系统应用的一些附加信息。

内容

本段所列组件用于支持Zynq SoC上的支持基于FPGA的no-OS系统:

- FPGA设计带有Microblaze CPU和openMAC IP核

- 双处理器共享内存库

- FAT16 SD卡访问库

- Zynq 第一阶段bootloader[FSBL] CMake工程

openPOWERLINK协议栈组件

下段包含一个Zynq SoC non-OS系统上的openPOWERLINK组件描述。

协议栈库

openPOWERLINK协议栈被分为用户和内核两部分。应用,运行于Zynq ARM之上,链接到应用库,该库使用双核共享内存库与内核驱动通信。该驱动与使用openMAC的驱动库连接来访问网络。它使用双处理器共享内存库与用户应用库通信,经由DDR3共享内存。

下列库适用于基于FPGA的系统:

stack/proj/generic/liboplkmnapp-dualprocshm(liboplkmnapp-dualprocshm.a)stack/proj/generic/liboplkmndrv-dualprocshm(liboplkmndrv-dualprocshm.a)

Demo应用

下列demo适用于Zynq SoC上基于FPGA的non-OS系统:

- [demo_mn_embedded] (\ref sect_components_demo_mn_embedded)

驱动

下列驱动适用于Zynq SoC上基于FPGA的non-OS系统:

- PCP Daemon on Microblaze

openPOWERLINK内核部分作为一个库被编译,并连接到后台程序。该后台程序作为POWERLINK通信处理器(PCP)。共享内存用于作为PCP和主处理器间的通信接口。PCP负责实现时序严格的处理以实现高性能低延迟。

驱动位于: drivers/xilinx-microblaze/drv_daemon

Bootloader

FPGA based non-OS systems on a Zynq SoC要求一个第一阶段Bootloader (FSBL)。FSBL配置FPGA带有一个HW位流(如果存在)并且从非易失存储器(NAND/NOR/QSPI)到RAM (DDR)加载操作系统(OS)映像或Standalone (SA)映像或第二阶段启动加载映像 ,然后执行之。支持多分区,每个分区可以是个代码映像或位流。 Zynq上为openPOWERLINK所用的FSBL被从Xilinx安装目录导入的工程文件编译到bootloader工程目录,并使用CMake配置文件将所需配置置入创建到bootloader。 按照下述步骤为demo编译Zynq FSBL:

打开一个配置了Xilinx ISE 14.7工具链的shell。

- Windows主机平台上打开

ISE Design Suite [64,32] Bit Command Prompt. - Linux主机平台上执行脚本

<ISE_ROOT_DIR>/settings[32,64].sh>配置当前shell。

- Windows主机平台上打开

创建可执行文件

> cd <openPOWERLINK_dir>/contrib/bootloader/xilinx-arm/fsbl/build > cmake -G"Unix Makefiles" -DCMAKE_TOOLCHAIN_FILE=../../../../../cmake/toolchain-xilinx-zynqarm-eabi-gnu.cmake .. -DCMAKE_BUILD_TYPE=[Debug,Release] > make all > make install

创建

创建openPOWERLINK用于Zynq SoC上的支持基于FPGA的no-OS系统,参考generic build instructions执行所有要求的创建步骤。并执行下列创建步骤:

运行openPOWERLINK

本段将展示用于Zynq SoC上的支持基于FPGA的no-OS系统的openPOWERLINK demos所需条件。

MN嵌入式demo

为了调试运行带有参考xapp1093的Xilinx SDK的Zynq MN demo。 (Debugging the Design, page 22).

MN 嵌入式demo可以使用Zynq板上的SD卡boot模式启动。 下述步骤用于板上启动MN demo:

打开

ISE Design Suite Command Prompt执行下述命令:> cd <openPOWERLINK_directory>\bin\generic\zynqarm\[BOARD_NAME]\[DEMO_NAME] > make all

*复制生成的BOOT.BIN文件到SD卡。

- 如果demo配置为使用CDC_ON_SD则复制配置文件(mnobd.cdc)。

- 使用终端程序查看debug输出(仅当应用编译为调试模式)

- Baud rate:

115200 - Data Bits:

8 - Stop Bits:

1 - Parity:

none - Flow control:

none

- Baud rate:

openPOWERLINK MN于Altera Nios II

介绍

在Altera FPGA上实现POWERLINK MN,可以使用基于Altera Qsys的IP核,提供openPOWERLINK协议栈功能,其目录位于

hardware/ipcore.

MN使用PCP (POWERLINK Communication Processor)和主处理器来执行openPOWERLINK内核和用户层。软核Altera Nios II被实例化为PCP,也可以作为主处理器。

以太网接口和最优POWERLINK控制器openMAC一起编译,能够实现低SoC延迟。此外,还能为菊花链网络应用提供hub功能。

两个处理器通过IP核的主接口连接,支持以下接口功能:

- Altera Avalon互联

- 外部(de-)多路复用地址/数据总线

内容

对于TERASIC DE2-115 INK板,下述MN FPGA设计可用:

- PCP和主设计放在一个单独的FPGA中 (驱动和应用):

hardware/boards/terasic-de2-115/mn-dual-hostif-gpio - PCP设计带有并行主接口(驱动实例):

hardware/boards/terasic-de2-115/mn-single-hostif-drv - 主处理器设计带有并行主接口(应用):

hardware/boards/terasic-de2-115/mn-single-hostif-gpio

注意,通过`hardware/ipcore/altera/qsys/mn[pcp|host]`里Qsys子系统实例重用,硬件设计很容易移植到其它平台!_

PCP和主处理器的软件工程被分入drivers和apps:

- PCP驱动后台任务:

drivers/altera-nios2/drv_daemon/build - 主"demo_mn_embedded":

apps/demo_mn_embedded/build/altera-nios2

要求

- Altera Quartus II v13.0 SP1 (Web Edition也可以)

- 该开发环境的使用经验。

- TERASIC_DE2-115开发版 (INK板)

- 可选:第二块TERASIC_DE2-115开发板 (INK板)

如果你想运行单独的FPGA demo。 - 可选:40线带状电缆用于连接两个INK板JP5 (长度尽量短)。

硬件安装

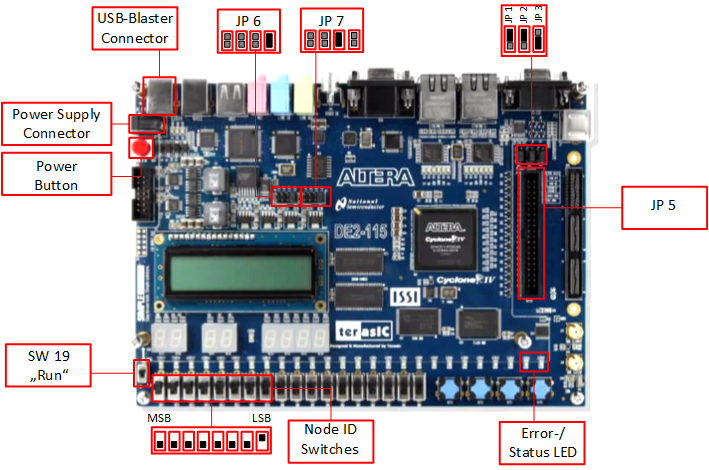

安装TERASIC_DE2-115 (INK)

- 从Terasic网站下载板子的用户手册

- 置跳线JP1, JP2, JP3, JP6 and JP7.

- 置开关SW 19到运行。

单独FPGA demo

- 连接INK板一个以太网口到POWERLINK网络。

- 按电源按钮(SW 18)给板子送电。

- 两个FPGA demo

- 连接一个INK板一个以太网口到POWERLINK网络。

- 确认两块板的JP6在同一位置(3.3V)。

- 40线扁平电缆连接两块板的JP5。

- 打开电源按钮(SW 18)给板子送电。

怎样build二进制文件

Altera Quartus II工程位于hardware/boards/[EVALBOARD]/quartus.

子目录带有mn-起始,都是关于设计POWERLINK MN demos。

步骤1-5用来在"Nios II Command Shell"执行$ make all。

- 打开你想使用的demo Quartus工程文件

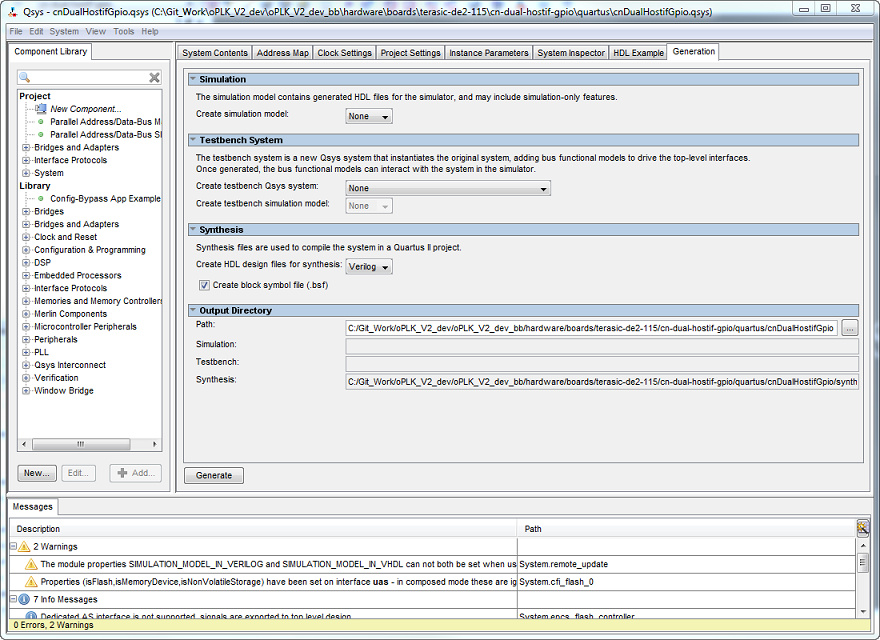

*.qpf于Altera Quartus II。 - 通过菜单Tools -> Qsys代开Qsys。

- 打开demo目录下的Qsys文件(

*.qsys),切换到Generation页并按下Generate按钮启动Nios II系统的生成。 - 生成结束(信息输出会显示)后关闭Qsys。

- 通过Quartus II窗体中的菜单Processing -> Start Compilation启动编译。

- 打开"Nios II Command Shell"

- Use the software design available in the openPOWERLINK subdirectory \n

apps/demo_mn_embedded/build/altera-nios2and \ndrivers/altera-nios2/drv_daemon/build. \n - 运行create-this-app脚本为驱动后台任务和应用任务创建Makefile。

$ ./create-this-app

注意:脚本默认使用the TERASIC DE2-115 dual MN demo (hardware/boards/terasic-de2-115/mn-dual-hostif-gpio/board.settings). 如果想切换到另一块板,使用--board选项:$ ./create-this-app --board [PATH-TO-BOARD] - 源代码更改后运行make来build ELF文件。

$ make - the Makefile also if the 如果Qsys中的Nios II设计被更改,需要重新创建Makefile。

$ ./create-this-app --rebuild - 如果想调试demo,使用

--debug选项。$ ./create-this-app --debug - 脚本帮助信息通过

--help打印。$ ./create-this-app --help

怎样运行demo

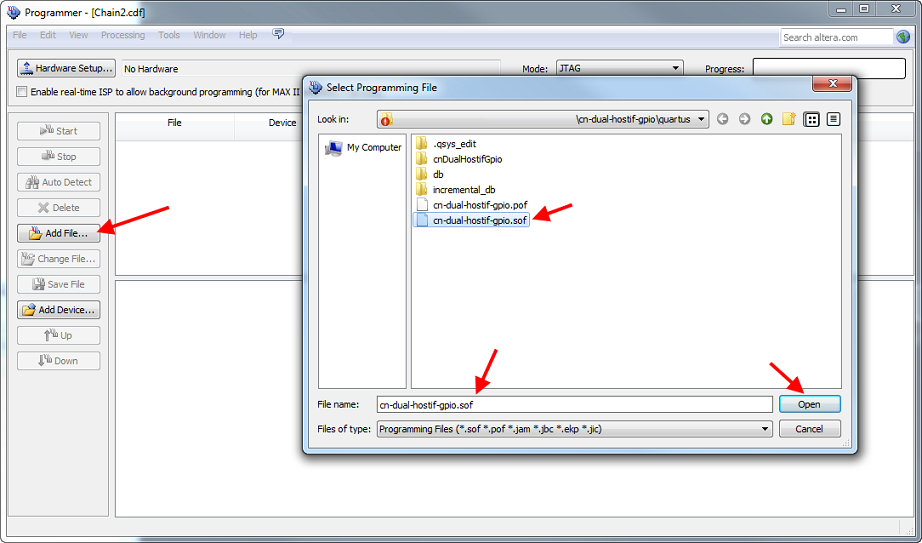

- 使用FPGA的Quartus II编程器来编写SOF文件。

它位于openPOWERLINK主目录的下列子目录:

hardware/boards/terasic-de2-115/mn-dual-hostif-gpio/quartus/*.sof

或hardware/boards/terasic-de2-115/mn-single-hostif-drv/quartus/*.sof和hardware/boards/terasic-de2-115/mn-single-hostif-gpio/quartus/*.sof

注意"Nios II Command Shell"里的$ make download-bits命令也会下载SOF! - 下载ELF到目标:

首先,总是按顺序下载PCP ELF文件,然后是主ELF。

这两个FPGA demos 都在"Nios II Command Shell"目录下$ make download-elf - 体验POWERLINK网络运行。

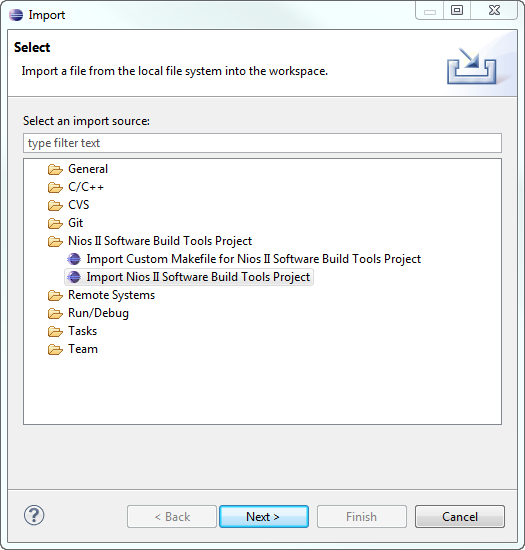

为Eclipse调试目的将工程导入Nios II Software Build Tools

要求:前一段怎样创建二进制文件步骤已完成。

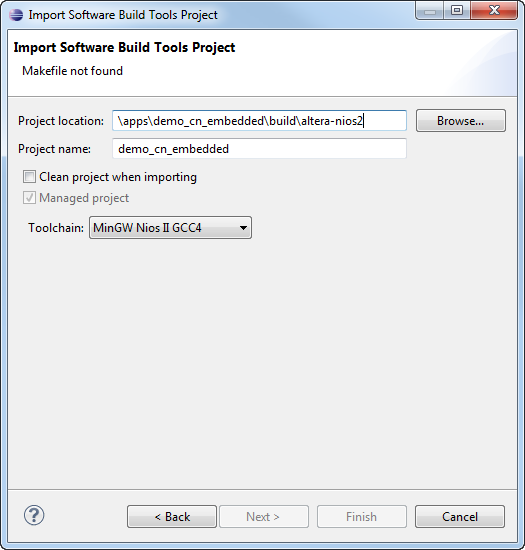

- 启动Nios II Software Build Tools for Eclipse

注意:推荐工作路径置于openPOWERLINK之外。 - 选择菜单File -> Import...

- 选择导入源Nios II Software Build Tools Project -> Import Nios II Software Build Tools Project

- 浏览

apps/demo_mn_embedded/build/altera-nios2(通过Browse...按钮) - 设置工程名为

demo_mn_embedded. - 按下按钮Finish.

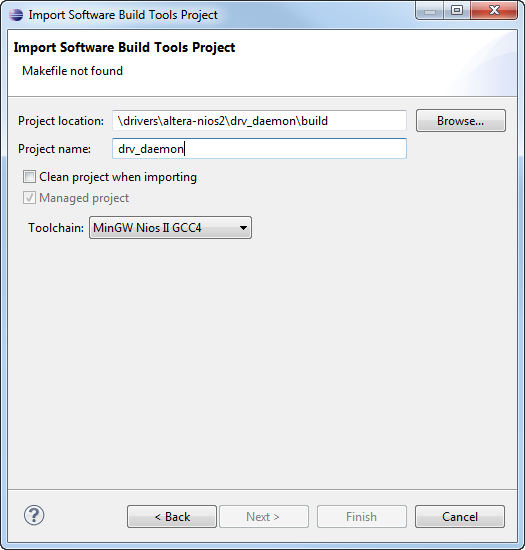

- 重复步骤2-6,使用路径

drivers/altera-nios2/drv_daemon/build和工程名drv_daemon。

怎样将程序写入flash

要求:前一段怎样创建二进制文件步骤已完成。

驱动(PCP)

驱动Nios II处理器被连接到EPCS flash控制器。EPCS存储了FPGA配置(.sof)和驱动软件(.elf)。按照下述方法创建和编程flash映像:

- 成功创建设计后使用makefile编程flash:

$ make program-epcs

App(Host)

主Nios II处理器装备了一个CFI flash,存储了软件software (.elf)。使用Nios II flash programmer tool下载映像到CFI flash。

- 成功创建设计后,打开Nios II flash programmer:

$ nios2-flash-programmer-gui - 选择SOPCINFO设计文件,包含主Nios II实例。

- 选择host_0_cpu_1作为主CPU名。

- 加入主处理器ELF (

demo_mn_embedded.elf)文件到文件列表。 - 确认到主Nios II实例的可用连接已建立。(使用

Connections...).

怎样使用MN配置文件

MN配置文件file mnobd.cdc需要存储于文件系统中。Nios II demos中没有文件系统,因而,需要生成mnobd_char.txt文件(\ref sect_openconfig_generate_char_file)。

注意事项

- 建议切换demo后清除所有生成文件。

- 下载PCP ELF文件总在主ELF文件前。

- 单独demo, 首先下载PCP's设计位流。

- Eclipse工程导入失败

确认Eclipse工作路径即不在makefile's目录下也不在其子目录下。 最好是将工作区放在openPOWERLINK源代码外面。openPOWERLINK CN于Altera Nios II上

介绍

在Altera FPGA上实现POWERLINK CN,可以使用基于Altera Qsys的IP核,提供openPOWERLINK协议栈功能,其目录位于

hardware/ipcore.

CN通过Altera Nios II软核处理器执行协议栈应用。以太网接口和最优POWERLINK控制器openMAC一起编译,能够实现较低的帧响应延时。此外,还能为菊花链网络应用提供hub功能。

两个处理器通过IP核的主接口连接,支持以下接口功能:

内容

对于TERASIC DE2-115 INK板,下述CN Quartus可用:

- 单处理器GPIO demo:

hardware/boards/terasic-de2-115/cn-single-gpio

双处理器GPIO demos: 两个处理器通过并口互联。运行设备主应用的处理器叫主。主作为第二内部Nios II处理器或外部位于第二TERASIC DE2-115板上的Nios II。

内部主处理器:

hardware/boards/terasic-de2-115/cn-dual-hostif-gpio

外部主处理器:

hardware/boards/terasic-de2-115/cn-single-hostif-drvhardware/boards/terasic-de2-115/cn-single-hostif-gpio- 注意,通过

hardware/ipcore/altera/qsys/cn_pcp里Qsys子系统实例重用,硬件设计很容易移植到其它平台!

主软件工程在apps中:

Host "demo_cn_embedded":

apps/demo_cn_embedded/build/altera-nios2

性能数据

- 最小循环周期: 400 us

- PReq-PRes延迟: 1 us

- 过程数据: 4 bytes input and 4 bytes output.

- 1 RPDO和1 TPDO可用。 禁止交叉通信。

要求和工具

开发板TERASIC_DE2-115 (INK板)

Altera Quartus II v13.0 SP1 (Web Edition也可以)

- Altera Nios II EDS v13.0 SP1

- Altera USB-Blaster驱动

https://www.altera.com/downloads/download-center.html#

\注意 联系本地Altera销售商获取Nios II IP核授权。使用Quartus II(生成一个*.sof文件)编译PCP FPGA需要该授权。在最终产品中,无需Nios II IP核授权来评估支持的例程设计。 - 有开发环境使用经验

- 带管理节点(MN)的POWERLINK网络

- openPOWERLINK管理节点,例如:Linux

- B&R POWERLINK管理节点

- other POWERLINK管理节点

TERASIC DE2-115 (INK)板硬件安装

运行POWERLINK从站需先搭建好TERASIC DE2-115。本章说明该板连入网络所需配置。

TERASIC_DE2-115(INK)搭建

可以从TERASIC网站下载用户手册获得主要信息。

PCP示例硬件设置

- 设置跳线JP1, JP2, JP3, JP6和JP7.

- 设置开关SW 19到Run.

- 用USB线将USB-Blaster连到你的PC上-参见在INK板上设置POWERLINK CN示例中的"USB-Blaster Connection".

- 将INK板上一个以太网端口连到一个POWERLINK MN上.

- 设置POWERLINK节点ID为'1': 将SW 10推到靠上的位置.

- 打开板子电源(SW 18按钮).

注意 现场应用要求CAT 5e电缆.

注意 所有I/O标准引脚电压是3.3 V. 不要将Vcc连到其它板上,但GND可以共地连接。

PCP扩展并口

有两个硬件例子可用<OPLK_BASE_DIR>/hardware/boards/terasic-de2-115

cn-single-hostif-drv \n 执行一个带16位(数据宽度)并口的PCP设计。主机和PCP之间数据交换通过共享内存完成。

cn-single-hostif-gpio \n 作为主机执行一个例程,准备连接到ink_pcp_16bitprll。 如果有两块TERASIC DE2-115板,此例特别有用。板子可以通过JP5针脚一个接一个的连在一起。

当使用16位并口时,下列JP5引脚(INK板载GPIO集JP5上的16位并行引脚)用于应用处理器的外部连接。

| PCP功能 | FPGA引脚 | Header引脚 | Header引脚 | FPGA引脚 | PCP功能 |

|---|---|---|---|---|---|

| HOSTIF_AD[0] | AB22 | 1 | 2 | AC15 | HOSTIF_AD[1] |

| HOSTIF_AD[2] | AB21 | 3 | 4 | Y17 | HOSTIF_AD[3] |

| HOSTIF_AD[4] | AC21 | 5 | 6 | Y16 | HOSTIF_AD[5] |

| HOSTIF_AD[6] | AD21 | 7 | 8 | AE16 | HOSTIF_AD[7] |

| HOSTIF_AD[8] | AD15 | 9 | 10 | AE15 | HOSTIF_AD[9] |

| don’t connect 5V to host ! | 11 | 12 | connect GND to host! | ||

| HOSTIF_AD[10] | AC19 | 13 | 14 | AF16 | HOSTIF_AD[11] |

| HOSTIF_AD[12] | AD19 | 15 | 16 | AF15 | HOSTIF_AD[13] |

| HOSTIF_AD[14] | AF24 | 17 | 18 | AE21 | HOSTIF_AD[15] |

| HOSTIF_AD[16] | AF25 | 19 | 20 | AC22 | |

| AE22 | 21 | 22 | AF21 | ||

| AF22 | 23 | 24 | AD22 | ||

| AG25 | 25 | 26 | AD25 | HOSTIF_BE[0] | |

| HOSTIF_BE[1] | AH25 | 27 | 28 | AE25 | |

| don’t connect 3.3V to host ! | 29 | 30 | connect GND to host! | ||

| AG22 | 31 | 32 | AE24 | ||

| AH22 | 33 | 34 | AF26 | ||

| HOSTIF_ALE_n | AE20 | 35 | 36 | AG23 | HOSTIF_CS_n |

| HOSTIF_WR_n | AF20 | 37 | 38 | AH26 | HOSTIF_RD_n |

| HOSTIF_ACK_n | AH23 | 39 | 40 | AG26 | HOSTIF_IRQ_n |

手动创建FPGA配置

本段描述使用Altera工具链生成FPGA位流。

POWERLINK评估板的demo软件位于POWERLINK Slave releasehardware/boards/terasic-de2-115目录。此目录包括了为不同应用支持所做的硬件配置。编译FPGA配置需遵守下述步骤:

打开Quartus II 13.0 SP1 (32/64-bit)

使用"File - Open Project"打开你的期望工程并选择设计路径: (例:

<OPLK_BASE_DIR>/hardware/boards/terasic-de2-115/cn-dual-hostif-gpio/quartus/<design_name>.qpf)打开Qsys (Tools - Qsys)

Qsys中打开相应的Qsys设计(File - Open)

Qsys中切换到"Generation" register点击"Generate"按钮,以便生成处理器系统的源文件

系统生成完成后可关闭Qsys,然后需要使用Quartus II生成FPGA配置。启动编译器并点击"Processing - Start Compilation".

编译完成后,Quartus会显示提示消息。

使用make创建FPGA配置

打开"Nios II Command Shell"

切换目录到期望的硬件工程(例:

<OPLK_BASE_DIR>/hardware/boards/terasic-de2-115/<hardware_design_name>/quartus)执行"make all"

FPGA配置用于驱动还是主机取决于例程(见下表)。

| design | 主机 | 驱动 |

|---|---|---|

| cn-single-gpio | x | |

| cn-dual-hostif-gpio | x | |

| cn-single-hostif-drv | x | |

| cn-single-hostif-gpio | x |

怎样为例程创建Makefiles

为所建系统编译和初始化期望的设计,需要提供一组脚本,每个脚本将创建一个Makefile。

用于主机处理器软件Makefile。

用于驱动处理器软件的Makefile(无需为"cn-single-gpio"设计).

怎样为主处理器例程软件创建Makefile

打开"Nios II Command Shell"

打开你的openPOWERLINK软件主机创建子目录。

<OPLK_BASE_DIR>/apps/demo_cn_embedded/build/altera-nios2运行脚本create-this-app为demo创建Makefile。

$ ./create-this-app脚本帮助

--help.$ ./create-this-app --help如果Nios II设计在Qsys中更改,重建Makefile。

$ ./create-this-app --rebuild用于调试目的,使用

--debug选项。$ ./create-this-app --debug注意 如果需要更换板子,使用

--board选项: option: 注意$ ./create-this-app --board [PATH-TO-BOARD]

切换源后运行make创建ELF文件。

$ make all

怎样为驱动例程创建Makefile

打开"Nios II Command Shell"

打开openPOWERLINK软件主机创建子目录。

<OPLK_BASE_DIR>/drivers/altera-nios2/drv_daemon/build运行脚本create-this-app为demo创建Makefile。

$ ./create-this-app该脚本帮助

--help.$ ./create-this-app --help如果Nios II设计在Qsys中被更改,重建Makdefile。

$ ./create-this-app --rebuild如果想调试demo,使用

--debug选项。$ ./create-this-app --debug注意 如果想更换板子,使用

--board选项: 注意$ ./create-this-app --board [PATH-TO-BOARD]

切换源后运行make创建ELF文件。

$ make all

怎样运行demo

按照下列build步骤在评估板上运行demo。

- 下载FPGA位流文件。

- 软件程序下到FPGA软核上。

- 将POWERLINK从站连接到POWERLINK网络。

编程bitstream为FPGA

有为FPGA编程itstream的程序:

使用Quartus II Programmer

使用Makefile

使用Quartus II编程

TERASIC_DE2-115 (INK)的SOF文件位于下述子目录:

<OPLK_BASE_DIR>/hardware/boards/terasic-de2-115/<hardware_design_name>/quartus/<hardware_design_name>.sof

打开Quartus v13.0 SP1

打开Quartus II编程器(Tools - Programmer)

添加*.sof文件用于下载

<OPLK_BASE_DIR>/hardware/boards/terasic-de2-115/<hardware_design_name>/quartus/<hardware_design_name>.sof

使用Makefile

打开"Nios II Command Shell"

切换目录到驱动或主机创建目录。

<OPLK_BASE_DIR>/drivers/altera-nios2/drv_daemon/build或

<OPLK_BASE_DIR>/apps/demo_cn_embedded/build/altera-nios2运行make download-bits下载bitstream。

$ make download-bits

为FPGA软核编译下载软件

打开"Nios II Command Shell"

切换目录到驱动或主机创建目录。

<OPLK_BASE_DIR>/drivers/altera-nios2/drv_daemon/build或

<OPLK_BASE_DIR>/apps/demo_cn_embedded/build/altera-nios2运行make download-elf下载软件。

如果以release模式创建软件:

$ make download-elf

或以debug模式使用:

$ make download-elf && nios2-terminal -i <instance USB-Blaster (1 or 0)>

将你的POWERLINK从站连入POWERLINK网络

建立POWERLINK网络。

体验系统运行。

注意 无Nios II license运行测试: 如果未指定可用Nios II IP核license,当在第二终端窗口执行软件时,原终端窗口不能关闭。Quartus programmer是有时间限制情况下的优先使用的编程*.sof工具。

怎样将工程导入Nios II EDS

为了能够使用"Nios II Software Build Tools for Eclipse",需要下述步骤倒入SWreference工程。

注意 在导入EDS工程前,需先生成Makefile。Makefile使用create-this-app创建。该脚本生成Makefile并初始化构建系统。在每次FPGA重新配置后,使用执行"--rebuild"选项重新创建。如果Makefile没有更新将打印错误消息。

注意 Makefile not up to date.

注意 `

注意 生成BSP要更新Makefile,然后再次build。

注意 从Eclipse生成:

1. 右键单击BSP工程。2. Nios II菜单中,点击生成BSP。

注意 从命令行生成:nios2-bsp-generate-file --settings=

导入Direct IO例程

打开Eclipse的Nios II EDS 13.0 SP1软件创建工具插件。

选择POWERLINK从站的新工作区。

Nios II EDS中点击"File - Import"

选择"Nios II Software Build Tools Project - Import Nios II Software Build Tools Project"并点击"Next"

下列导入对话框选择

<OPLK_BASE_DIR>/apps/demo_cn_embedded/build/altera-nios2目录。

选择适当的工程名(例:"DirectIO")并设置"MinGW Nios II GCC4"(Windows默认)或"Linux Nios II GCC4"(Linux默认)作为工具链。

点击"Finish"按钮。

为了确认所有路径,需要从Nios II EDS再次rebuild软件,以便在build过程中解析这些路径并输出"make"。参考下一章获得更多关于"make"build过程信息。

导入双处理器例程

当选用双处理器例程时,上述步骤也同样需要。本例,需导入下述目录。

<OPLK_BASE_DIR>/drivers/altera-nios2/drv_daemon/build

<OPLK_BASE_DIR>/apps/demo_cn_embedded/build/altera-nios2

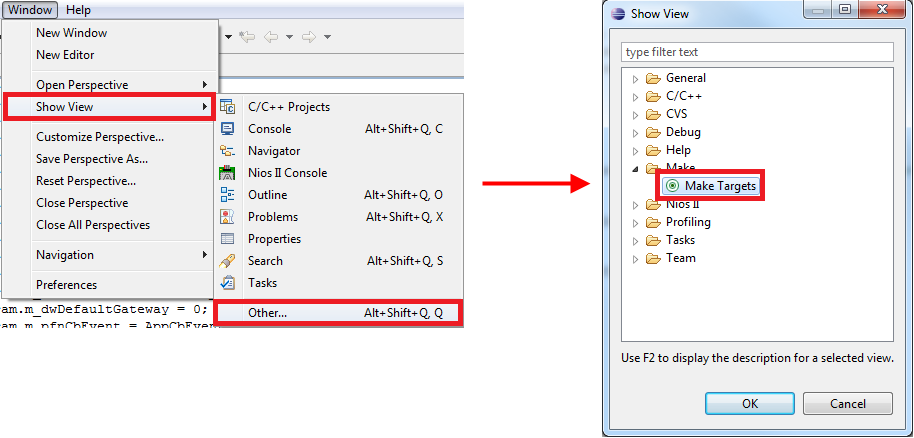

Nios II EDS中软件编译使用make

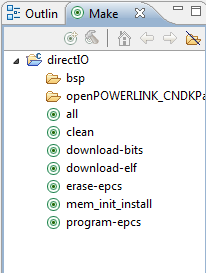

为了方便从"Nios II EDS"中执行Makefile。"Make Target"视图需有效。下述步骤告诉我们怎么做。

- 在带有你的导入工程的EDS中点击"Window - Show View - Other"

2.在"Make"类别下选择"Make Target"。

一个新窗体将在EDS窗体底部显示。该视图中,可以从下表中添加未make的目标。然而,不是所有工程都支持所列make目标。

下表给出了所有可用make目标的详细描述。

| 目标 | 描述 |

|---|---|

| all | 重编译软件更改部分并链接生成.elf二进制文件 |

| clean | 清除所有生成文件 |

| download-bits | 下载bitstream到目标 |

| download-elf | 下载软件到Nios II处理器 |

| erase-epcs | 擦除本地EPCS flash设备 |

| program-epcs | 将生成的flash映像烧写入本地EPCS flash |

怎样烧写本地flash

要求:前面章节怎样创建二进制文件所述步骤已完成。

- 成功创建design后,使用makefile烧写flash:

$ make program-epcs

注意事项

- 切换demo后建议清除所有已生成文件。

- Eclipse工程导入失败

确认Eclipse工作区即不在本地makefile目录也不在其子目录。 最好是将工作区置于openPOWERLINK源代码目录之外。openPOWERLINK于Altera Cyclone V SoC上

介绍

openPOWERLINK运行于Altera Cyclone V SoC之上,其时序要求严格的内核部分协议栈运行在Nios II软核处理器的programmable logic (PL)段内。用户部分协议栈运行于ARM Cortex A9 Core 0,位于硬处理系统(HPS)段内。

以太网接口由优化的POWERLINK控制器openMAC创建,其能够实现较低的SoC延迟。另外,还为菊花链网络提供一个实现hub功能的IP核。

双处理器采用共享内存接口互通。

内容

下述MN硬件设计可用于Altera Cyclone V SoC板:

- PCP于PL中并且主机置于HPS(驱动和应用)的ARM Cortex A9 core 0上:

hardware/boards/altera-c5soc/mn-soc-shmem-gpio

PCP软件工程和主机处理器分别在drivers和apps中:

- PCP驱动后台任务:

drivers/altera-nios2/drv_daemon/build - 主机"demo_mn_embedded":

apps/demo_mn_embedded/build/altera-c5socarm

要求

- Altera Quartus II v14.0.200 (Web Edition也可以)

- 有相关开发环境使用经验。

- Altera Cyclone V SoC开发板。

- [CMake] (\ref sect_build_cmake)

- 通过串口显示ARM Cortex A9调试打印信息的软件终端。

硬件安装

为Altera Cyclone V SoC开发板安装。

- 根据Altera页面设置跳线和开关。

(章节3–1。开关位置和默认设置,12页)

- 将 Cyclone V SoC开发板上任一"Dual Ethernet port"连到POWERLINK网络。

怎样创建二进制文件

生成硬件

Cyclone V SoC的Altera Quartus II工程位于hardware/boards/altera-c5soc/mn-soc-shmem-gpio/quartus.

步骤1-5可以在"Nios II Command Shell"中通过执行$ make all完成。

- Altera Quartus II中打开Quartus工程文件

mn-soc-shmem-gpio.qpf。 - 通过菜单Tools -> Qsys打开Qsys。

- 打开demo目录下的Qsys文件(

mnSocShmemGpio.qsys),按下按钮Generate生成主机和PCP系统。 - 生成完成后关闭Qsys(信息输出显示)。

- 通过Quartus II窗体中的菜单Processing ->Start Compilation启动编译。

创建驱动后台任务

为Altera Cyclone V SoC build驱动后台任务遵循下列步骤:

- 打开"Nios II Command Shell".

- 使用openPOWERLINK子目录下可用的软件设计

drivers/altera-nios2/drv_daemon/build. - 运行脚本create-this-app来创建驱动后台任务所需的Makefile。

$ ./create-this-app --board ../../../../hardware/boards/altera-c5soc/mn-soc-shmem-gpio - 源代码更改后运行make以build ELF文件。

$ make - 运行下述命令生成后台程序和FPGA启动文件。

$ make fpgaboot

需要一些附加命令来rebuild, debug和获取帮助信息。

- Qsys中的Nios II设计更改后,使用下述命令rebuild Makefile。

$ ./create-this-app --rebuild --board ../../../../hardware/boards/altera-c5soc/mn-soc-shmem-gpio - 想调试demo,使能NIOS II打印,使用

--debug选项。$ ./create-this-app --debug --board ../../../../hardware/boards/altera-c5soc/mn-soc-shmem-gpio - 脚本的帮助消息通过

--help打印。$ ./create-this-app --help

创建嵌入式MN demo应用

为Altera Cyclone V SoC build嵌入式MN demo应用,请参考生成build指令,使用CMake并执行以下步骤:

- [创建硬件库和预加载器] (\ref sect_build_hardware_build_altera_arm)

- [创建协议栈库] (\ref sect_build_stack_build_c5socarm-altera)

- 创建你的应用(或一个已提交的demo应用)

怎样运行demo

Altera Cyclone V SoC板上的MN嵌入式demo可以使用SD卡启动模式启动。 板子上的MN demo启动步骤:

- 打开一个"SoC command shell".

- 准备一张SD卡,然后使用下述命令连接:

cd <openPOWERLINK_directory>\bin\generic\alterac5arm\altera-c5soc\mn-soc-shmem-gpiodd if=<Altera_installation_dir>/embedded/embeddedsw/socfpga/prebuilt_images/sd_card_linux_boot_image.img of=/dev/<sd_card_drive>alt-boot-disk-util.exe -p preloader-mkpimage.bin -a write -d <sd_card_path> bs=1M

- 复制

BOOT.bin和fpga.rbf从<openPOWERLINK_directory>\bin\generic\alterac5arm\altera-c5soc\mn-soc-shmem-gpio到SD卡上。 - 从准备的SD卡上启动Altera Cylcone V SoC。

- 体验运行POWERLINK网络。

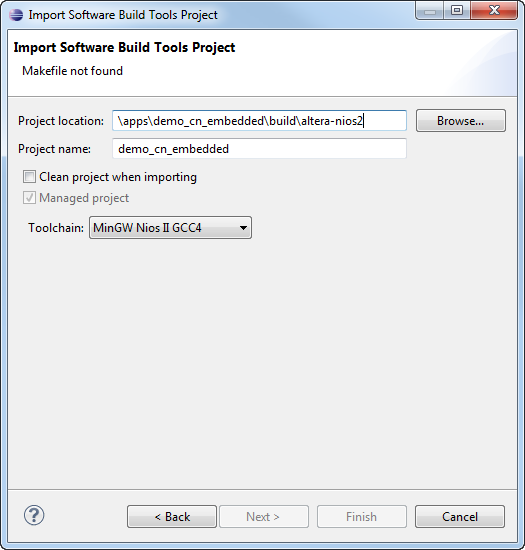

出于调试目的为Eclipse的Nios II软件创建工具导入工程

要求:怎样创建二进制文件段落中的步骤已完成。

- 启动Nios II Software创建工具的Eclipse插件。

注意:建议将工作区放在openPOWERLINK目录之外。 - 选择菜单File -> Import...

- 选择导入源Nios II Software Build Tools Project -> Import Nios II Software Build Tools Project

- 浏览到

drivers/altera-nios2/drv_daemon/build(通过按钮 Browse...) - 设置工程名为

drv_daemon。 - 按下Finish按钮。

为DS5调试目的怎样将工程倒入Eclips

条件:怎样创建二进制文件段所述步骤已走完。

- 启动一个"SoC embedded shell".

- 使用下述命令启动支持DS5的Eclipse:

$ eclipse - 选择菜单File -> Import...

- 选择导入源General -> Existing Project into Workspace

- 浏览到

<openPOWERLINK_directory>(通过按钮Browse...) - 选择

demo_mn_embedded工程。 - 按下按钮 Finish.